Меню

+7 (495) 785-95-25

sale@lcard.ru

sale@lcard.ru

В данной статье рассматриваются вопросы минимизации задержек ввода-вывода данных при реализации real-time задачи на основе крейта LTR. А именно, рассматриваются факторы задержек, обусловленные архитектурой LTR.

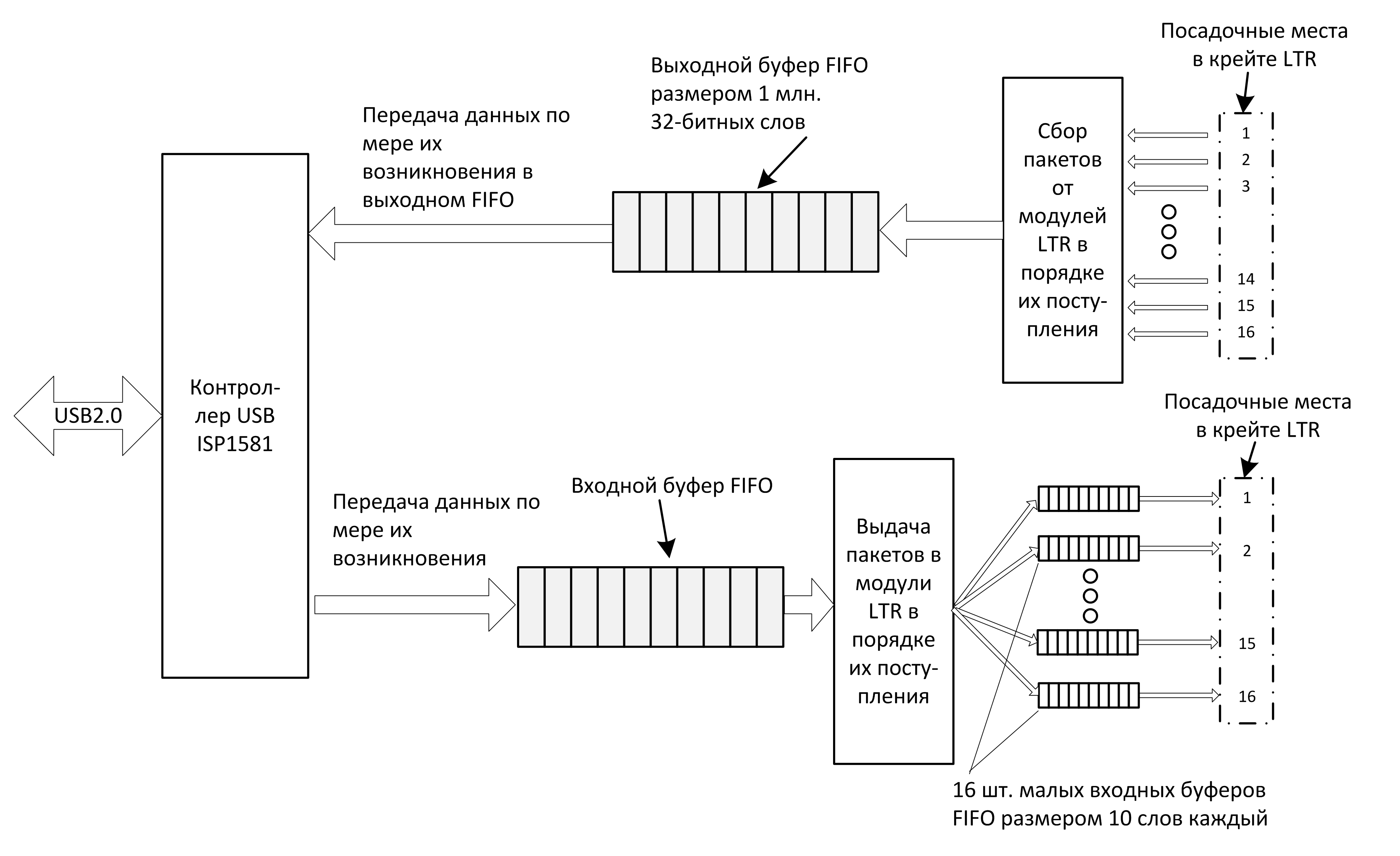

Архитектура крейта LTR описана в руководстве (глава 4), и ключом для её понимания является нижеприведённый рисунок (с точностью до реализации показанных общих принципов в разных крейтах и различий в интерфейсах с ПК):

Исходя из рисунка:

а) в поток на вывод не ставить более 10-ти слов подряд (слово - 32 бита), адресованных одному и тому же модулю LTR (в данном посадочном месте крейта);

б) средняя скорость посылки данных одному модулю LTR не должна быть выше пропускной способности этого модуля на вывод.

Пропускная способность (п.4.6.3.7 руководства) на вывод (или приём команд) у модулей LTR разная, например, и у модулей LTR41 - LTR43 она составляет 80‑Кбайт/с, или в пересчёте на слово – 20 Кслов/c, а у большинства остальных – 1,6 Мбайт/c (Примечание 1).

В частности, если условия a), б) не выполняются, то на рисунке выше данные во "входном буфере FIFO" будут сильно копиться из-за того, что соответствующий "малый входной буфер FIFO" одного из модулей будет часто полным и вывод на остальные модули из-за этого будет тормозиться.

К значимым факторам задержек на уровне модулей LTR относятся:

Заметим, что минимальной задержкой на ввод обладает модуль АЦП LTR11 с АЦП последовательного приближения, широкой полосой частот пропускания и без буферизации на уровне модуля. Но в многоканальном режиме LTR11 имеет "коммутационную задержку", хотя процесс последовательного опроса каналов LTR11 создаёт фазовый сдвиг момента оцифровки АЦП, а не задержку в тракте преобразования.

Примечание 1: В рамках развития системы LTR (или заказа) возможна модернизация модулей LTR42, LTR43 на быстрый интерфейс вывода, возможно распараллеливание буферизации на вывод в крейт-контроллере LTR и другие пути развития системы LTR в сторону оптимизации real-time задач.

По данной теме читайте также следующие статьи:

| Перейти к другим статьям FAQ | Cтатья создана: | 17.12.2016 |

| Последняя редакция: | 30.06.2017 |

Адрес: 117105, Москва, Варшавское шоссе, д. 5, корп. 4

Многоканальный телефон:

+7 (495) 785-95-25

Отдел продаж: sale@lcard.ru

Техническая поддержка: support@lcard.ru

Время работы: с 9-00 до 19-00 мск

+7 (495) 785-95-25

+7 (495) 785-95-25 sale@lcard.ru

sale@lcard.ru