Меню

+7 (495) 785-95-25

sale@lcard.ru

sale@lcard.ru

Страницы 1

Выяснил одну особенность передачи данных по USB:

если перед вызовом X502_Send вызвать функцию X502_OutGetStatusFlags,

то периодическая задержка через 128 отсчетов пропадает.

Таким образом, код передачи у меня выглядит так:

X502_PrepareData(hnd, NULL,NULL, BufToSend,m_SendSize , 0, out_buf);

X502_OutGetStatusFlags(hnd,&status);

X502_Send (hnd, out_buf,m_SendSize, 0);

Однако, редкие задержки (через 10-12 минут), как при передаче по Ethernet,

остаются.

Прошу объяснить эту особенность

Имеются ввиду не коды прошивок, а исходники

Спасибо, утилитами обновления прошивок я пользовался.

А сами прошивки вы выкладываете где-нибудь?

А прошивки ПЛИС для L-502 и E-502 выложены где-нибудь?

Синхроимпульсы идут постоянно.

В буфере мы передаем 1024 байта. Начало и конец

каждого буфера заполнены нулями.

Задержки происходят, когда весь буфер еще не передан.

Это видно из картинок. Сбои происходят во время передачи!

Правильно, после передачи 1024 байт буфер опустошается и,

поскольку импульсы продолжаются, выводится последний отсчет -

нуль.

Мы передаем данные на вывод с частотой, значительно меньшей, чем они выводятся.

В пересчете на период синхроимпульсов длина буфера составляем 7.8 миллисекунд,

а таймер вывода буфера работает с интервалом 50 миллисекунд. Так что речи о переполнении

быть не может.

Код вывода для Ethernet и USB интерфейсов одинаков. Весь буфер выводится одной командой

X502_Send.

При работе по Ethernet теряются первые байты передаваемых данных.

Также выяснилось, что каждые 11-12 минут непрерывной работы по Ethernet бывают потери

синхроимпульсов различной длительности через несколько миллисекунд от начала буфера.

Картинку сбоев постараюсь сделать завтра.

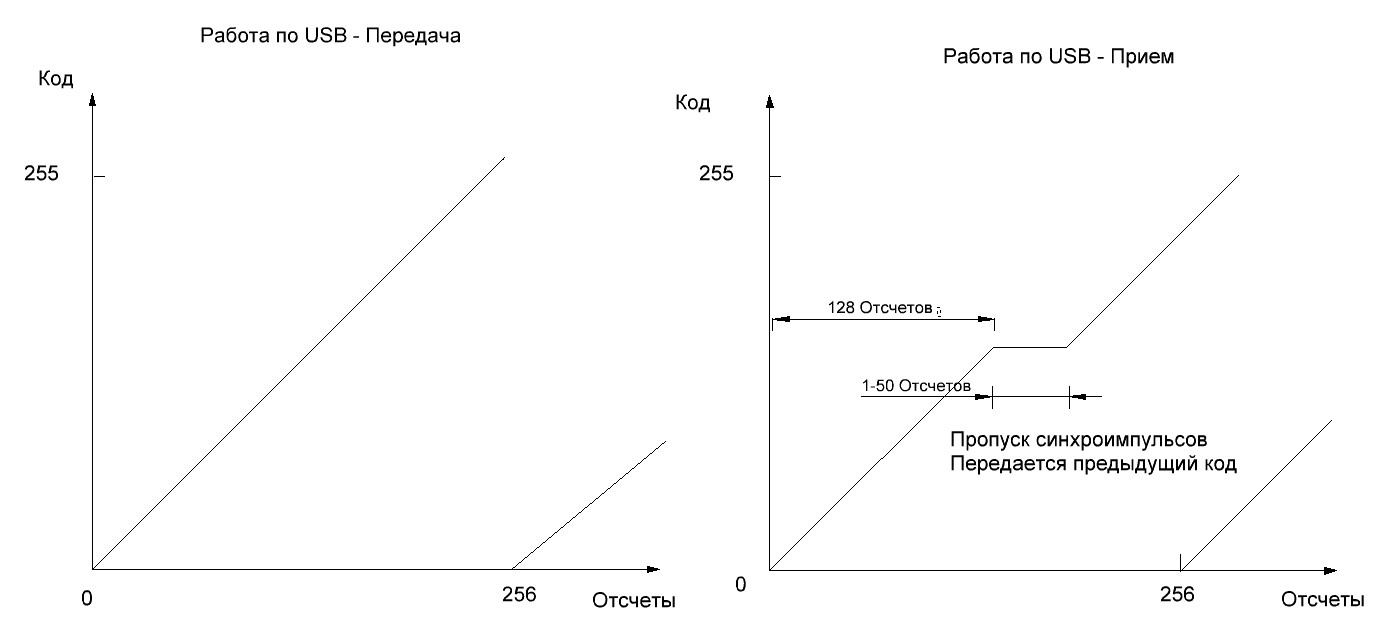

При работе по USB следует обратить внимание, что время начала сбоя (пропуска синхроимпульсов)

фиксировано!

Это тема является продолжением темы

https://www.lcard.ru/forums/viewtopic.php?id=10446

Поскольку программное обеспечение платы L-502 в настоящее время

не позволяет осуществить синхронный цифровой вывод DO по внешнему

синхроимпульсу, мы решили попробовать реализовать нужный нам режим

при помощи устройства E-502.

Используем E-502 со следующими параметрами:

ПЛИС 2

PLDA 0.15

ARM 1.0.21.0

SDK от 01.11.21 Версия 1.1.21

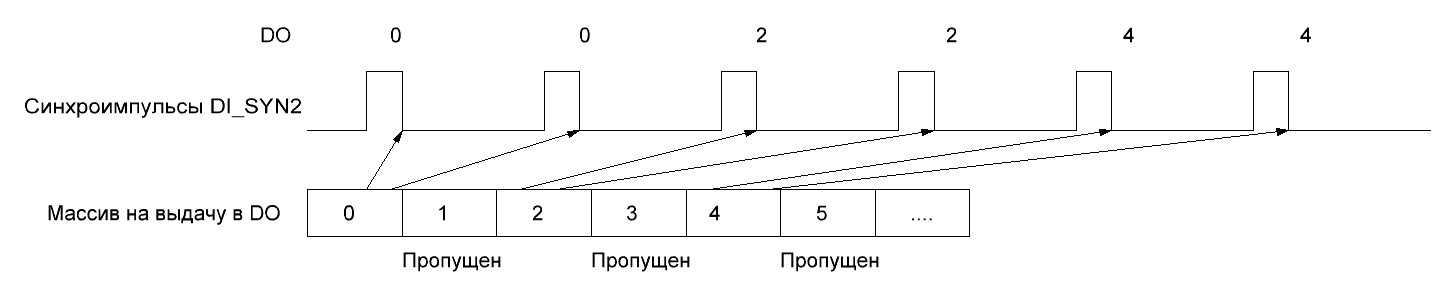

Нам нужно, чтобы по каждому синхроимпульсу DI_SYN2 на

цифровой выход выдавался один отсчет из буфера.

Код инициализации синхронного цифрового вывода (кратко, без обработки ошибок):

X502_SetSyncMode(hnd,X502_SYNC_DI_SYN2_FALL);

X502_SetSyncStartMode(hnd,X502_SYNC_INTERNAL);

X502_SetExtRefFreqValue(hnd,131072);

X502_SetOutFreqDivider (hnd,1);

X502_StreamsEnable(hnd,X502_STREAM_DOUT);

X502_Configure(hnd, 0);

X502_StreamsStart(hnd);

По таймеру формируем буфер из 1024 байт, в котором

следующий байт на 1 больше предыдущего.

Код на вывод:

Вывод данных делается по таймеру:

uint32_t BufToSend[65535];

uint32_t out_buf[65535];

// Заполняем BufToSend

....

X502_PrepareData(hnd, NULL,NULL, BufToSend,m_SendSize , 0, out_buf);

X502_Send (hnd, out_buf,m_SendSize, 0);

При работе через USB получаем:

периодически ровно через 128 отсчетов от начала передаваемого буфера

(что соответствует длительности примерно 1 млсек от начала буфера)

происходят пропуски синхроимпульсов длиной от 1 до 50 отсчетов.

См. рисунок.

При работе через Ethernet картина другая. Сбои происходят намного

реже - с периодом несколько секунд. Пропуск синхроимпульса происходит

через 1-2 отсчета от начала буфера, длительность сбоя - 3 отсчета.

Чтобы игнорировать пропусти первых синхроимпульсов

мы сделали 4 первых отсчета пустыми (заполнили нулем).

Можно ли как то доработать ПО E-502, чтобы режим передачи по USB

заработал?

В Вашем случае X502_SetExtRefFreqValue() служит только для того, чтобы сказать библиотеке, что Вы работаете на частотах до 700 КГц и установка делителя 1 допустима, в общем больше это не влияет на работу.

Так вроде должно работать.

Вроде должно выло работать, но для L-502 не заработало.

Вот и сделайте, что бы заработало

Причем здесь архитектура плат - была возможность настроить систему под свою задачу.

Посмотрите переписку выше- я понял, что до частоты 700 кГц синхронный вывод

должен был заработать

Лет 10 назад я доработал BIOS для PCI плат L-760-780 и реализовал нужный

режим цифрового вывода.

Лет 15 назад я делал то же самое для цифрового ввода...

Для платы L-502 я не имею доступа к исходникам и прошивке не могу ничего сделать...

А шина PCI почти ушла...

И что здесь нештатное- выводить цифровые данные по внешнему синхросигналу?

Voleg пишет:...И все-таки в чем причина неправильной выборки отсчетов из буфера?

В том, что этот нештатный режим не отлаживался в FPGA (и ранее не тестировался в x-502), а заработать мог только чудом. Отладка и полноценное внедрение этого режима предполагает конкретный пласт работ по проекту x-502 - об этом я писал выше. Вопрос планирования этих работ обсудите с нашим отделом продаж. За рамки обычной техподдержки этот вопрос уже вышел, как я понимаю.

Уважаемые сотрудники L-card!

Я сотрудничаю с Вами с 1999 года и всегда получал оперативную

поддержку при работе над различными проектами.

При моем участии было приобретено более 70-ти устройств L-Card.

Что же получается в итоге нашей переписки:

Для платы L-502 частота цифрового вывода снижена ЦАП и DO в два раза по

сравнению с частотой ввода АЦП и DI.Возможно, это сделано из-за того,

что плата не успевает обработать одновременный ввод и вывод с большой частотой.

Например, мне надо по внешнему сигналу вводить данные с АЦП с частотой 1Гц

и выводить цифровые данные DO с той-же частотой. Так вот, это не получится!

Цифровой вывод будет осуществлятьcя раз в две секунды.

У пользователей вашей продукции разные задачи!

Не всем потребителям нужно выводить 2 млн слов в секунду!

Для нашей задачи это совсем не нужно!

Теперь вы говорите, что с вами надо заключить договор на доработки,

которые (я уверен) составляют несколько строк кода, чтобы реализовать

нормальный режим цифрового вывода - запрос- ответ.

Просто сделайте это. В документации отметьте, что этот режим работает

только для определенных частот и т.д.

Кроме того, получается, что L-502 и E-502 работают по разному,

хотя вы заявляете об унификации.

Надеюсь на понимание...

Попробовал на L-502, похоже на ней действительно отличается, все также как у Вас, вне зависимости от версии прошивки (только версии все же у Вас видимо PLD - 0, а FPGA - 0.10).

Так что сейчас работает только на E-502 как описал выше.

И все-таки в чем причина неправильной выборки отсчетов из буфера?

Надо искать ошибку в прошивке прошивке самой платы или в SDK?

И можно ли это сделать?

В x502api.pdf (пункт 4.3.4.8) в описании функции X502_SetOutFreqDivider написано:

Для модуля L-502, чтобы была возможность установить делитель, отличный

от X502_OUT_FREQ_DIV_DEFAULT, необходимо обновить прошивку ПЛИС до вер-

сии 0.5 или выше.

У нас прошивка версии 0.

Может ли это быть причиной пропуска передачи отсчетов из буфера?

Проверили выдачу с новым SDK и установили X502_SetExtRefFreqValue и X502_SetOutFreqDivider.

Для теста выдаем буфер байт в котором каждый следующий отсчет больше предыдущего на 1.

Теперь данные выдаются с частотой синхроимпульсов, но буфер выбирается через один синхроимпульс.

По картинке видно, что на выдачу пропускаются каждые четные отсчеты

Да по поводу приведенного куска кода, PreloadStart вообще по идее должен делаться уже после Configure().

Также лучше сделать загрузку первого блока данных на вывод после Preload но до StreamsStart, в этом случае при запуске потоковой генерации модуля данные уже будут загружены в его буфер, и не будет некой зависимости от неопределенной ситуации - что первым придет на модуль после старта - импульс на SYN2 или данные из ПК.

И "Вывод данных делается по таймеру" не до конца понятно, как устанавливаете таймер, ведь Вы до конца не знаете частоту, с которой будут выводиться слова.

Хорошо, я сделаю загрузку первого блока данных.

Насчет отправляемых данных - блоки данных поступают по таймеру, период которого может меняться.

Каждому байту данных добавляются биты достоверности.

После каждого блока данных устанавливаются соответствующие биты - данные недостоверны.

Эти биты "висят" на выходном порту и забираются устройством сбора, пока не придет новый блок.

Для него будут установлены биты - данные достоверны.

Не совсем понял зачем устанавливать сигнал опорной частоты, если используется внешняя синхронизация.

Будет ли работать такой код инициализации:

X502_SetSyncMode(hnd,X502_SYNC_DI_SYN2_FALL);

X502_SetSyncStartMode(hnd,X502_SYNC_DI_SYN2_FALL);

X502_SetExtRefFreqValue(hnd, 250000);

X502_SetOutFreqDivider(hnd, 1);

X502_StreamsEnable(hnd,X502_STREAM_DOUT);

X502_PreloadStart(hnd);

X502_Configure(hnd, 0);

X502_StreamsStart(hnd);

Вывод данных делаем по таймеру:

uint32_t BufToSend[65535];

uint32_t out_buf[65535];

// Заполняем BufToSend своими данными:

....

// Готовим

X502_PrepareData(hnd, NULL,NULL, BufToSend,m_SendSize , 0, out_buf);

// Посылаем

X502_Send (hnd, out_buf,m_SendSize, 0);

Нет, это синхронный вывод!

Вод код инициализации (кратко- без обработки ошибок):

X502_SetSyncMode(hnd,X502_SYNC_DI_SYN2_FALL);

X502_SetSyncStartMode(hnd,X502_SYNC_DI_SYN2_FALL);

X502_StreamsEnable(hnd,X502_STREAM_DOUT);

X502_PreloadStart(hnd);

X502_Configure(hnd, 0);

X502_StreamsStart(hnd);

Вывод данных делается по таймеру:

uint32_t BufToSend[65535];

uint32_t out_buf[65535];

// Заполняем BufToSend:

....

X502_PrepareData(hnd, NULL,NULL, BufToSend,m_SendSize , 0, out_buf);

X502_Send (hnd, out_buf,m_SendSize, 0);

Давайте сначала...

У меня есть внешний источник синхроимпульсов, подключенный к выводу DI_SYN2 внешнего сигнального разъема.

Он может поступать с разной частотой и длительностью.

По падению уровня этого сигнала я должен вывести на выводы DO один отсчет из своего

буфера. По первому импульсу DI_SYN2 выводится первый отсчет, по второму импульсу DI_SYN2 следующий

отсчет из буфера не выводится, третий отсчет выводится и т.д. Таким образом я не могу реализовать

необходимый протокол обмена с внешним устройством.

Вы хотите сказать, что как-то можно удвоить частоту синхроимпульса?

Мне нужно простое решение - по каждому синхроимпульсу должен выводится один отсчет DO из буфера

А сколько синхронных линий данных на вывод требуется? Если менее 16-ти, то одну из линий данных можно использовать как сигнал синхронизации, обновляя состояние этой линии кратно более чаще, чем остальные линии данных. Это позволит организовать синхронный вывод на шине данных до 500 кГц, если данные будут, например, обновляться, по фронту сигнала синхронизации, а дублировать предыдущие значения - по спаду.

Непонятно, как это сделать штатными средствами L-502 API

Надеемся, у Алексея получится запустить нужный нам режим.

Что касается отдельной версии изделия, наша фирма не готова оплачивать разработку.

Нас устроит отдельная прошивка, где реализован цифровой вывод без прореживания

К сожалению, мы не может изменить систему сбора информации, выдающую синхросигнал.

Нам нужен только режим вывода с частотой tref.

При этом вывод на ЦАП и ввод с АЦП и DI мы не используем.

Мы согласны на уникальную прошивку платы, где реализован необходимый нам режим.

Где-то 262 тыс отсчетов в секунду

На базе платы L-502 (прошивка ПЛИС -0, прошивка BlackFin -0.10 )

мы разрабатываем систему синхронного цифрового вывода.

В качестве синхронизации используется внешний источник X502_SYNC_DI_SYN2_FALL.

Однако, согласно Руководству пользователя, п.3.4.4 (Каналы цифрового вывода и ЦАП) и

п. 3.8.8 (Относительные задержки каналов АЦП, ЦАП и каналов ввода-

вывода) цифровой вывод DO производится только с периодом 2*tref, в отличие от

цифрового ввода и ввода АЦП, где период ввода tref.

Для реализации нашей системы необходимо, чтобы цифровой вывод осуществлялся

на каждом импульсе опорного синхросигнала CONV_OUT, т.е. с периодом tref.

Вопрос1.

Можно ли реализовать синхронный цифровой вывод данных с периодом tref,

используя штатную прошивку платы?

Вопрос 2.

Если использовать штатную прошивку платы нельзя, можно ли сделать специальную

прошивку, реализующую необходимый нам режим?

При этом вывод на ЦАП, ввод АЦП и DI нам не нужен

Страницы 1

Адрес: 117105, Москва, Варшавское шоссе, д. 5, корп. 4

Многоканальный телефон: +7 (495) 785-95-25

Письма и запросы: lcard@lcard.ru

Отдел продаж: sale@lcard.ru

Мы работаем с юридическими и физическими лицами, пожалуйста, прикладывайте реквизиты при оформлении заказа

Техническая поддержка: support@lcard.ru

Время работы: с 9-00 до 19-00 мск